Charles J. Alpert and Andrew B. Kahng

UCLA Computer Science Department, Los Angeles, CA 90024-1596

## Abstract

This survey describes research directions in netlist partitioning during the past two decades, in terms of both problem formulations and solution approaches. We discuss the traditional min-cut and ratio cut bipartitioning formulations along with multi-way extensions and newer problem formulations, e.g., constraint-driven partitioning (for FPGAs) and partitioning with module replication. Our discussion of solution approaches is divided into four major categories: move-based approaches, geometric representations, combinatorial formulations, and clustering approaches. Move-based algorithms iteratively explore the space of feasible solutions according to a neighborhood operator; such methods include greed, iterative exchange, simulated annealing, and evolutionary algorithms. Algorithms based on geometric representations embed the circuit netlist in some type of "geometry", e.g, a 1-dimensional linear ordering or a multi-dimensional vector space; the embeddings are commonly constructed using spectral methods. Combinatorial methods transform the partitioning problem into another type of optimization, e.g., based on network flows or mathematical programming. Finally, clustering algorithms merge the netlist modules into many small clusters; we discuss methods which combine clustering with existing algorithms (e.g., two-phase partitioning). The paper concludes with a discussion of benchmarking in the VLSI CAD partitioning literature and some perspectives on more promising directions for future work.

# 1 Introduction

The essence of netlist partitioning is to divide a system specification into clusters such that the number of intercluster connections is minimized. The partitioning task is ubiquitous to many subfields of VLSI CAD: any top-down hierarchical (i.e., "divide and conquer") approach to system design must rely on some underlying partitioning technique. There are several reasons why partitioning has recently emerged as a critical optimization in many phases of VLSI system synthesis, and why the past several years have seen so much research activity on the subject.

Above all, partitioning heuristics are used to address the increasing complexity of VLSI design. Systems with several million transistors are now common, presenting instance complexities that are unmanageable for existing logic-level and physical-level design tools. Partitioning divides a system

<sup>\*</sup>Partial support for this work was provided by NSF Young Investigator Award MIP-9257982.

into smaller, more manageable components; the number of signals which pass between the components corresponds to the interactions between the design subproblems. In a top-down hierarchical design methodology, decisions made early in the system synthesis process (e.g., at the system and chip levels) will constrain succeeding decisions. Thus, the feasibility – not to mention the quality – of automatic placement, global routing and detailed routing depends on the quality of the partitioning solution. A bottom-up clustering may also be applied to decrease the size of the design, typically in cell- or gate-level layout. The current emphasis on a quick-turnaround ASIC design cycle reinforces the need for reliable and effective algorithms.

Partitioning heuristics also have a greater impact on system performance as designs become interconnect-dominated. In current submicron designs, wire delays tend to dominate gate delays [15]; the differences between on-chip and off-chip signal delays and the increasingly pin-limited nature of large chips make it desirable to minimize the number of signals traveling off a given chip. Larger die sizes imply that long on-chip global routes between function blocks will more noticeably affect system performance. Other considerations (e.g., design for testability, low-power design, etc.) also require partitioning algorithms to identify interconnect structure, albeit at more of a functional or communication-based level.

Finally, partitioning heuristics affect the layout area: wires between clusters at high levels of the hierarchy will tend to be longer than wires between clusters at lower levels, and total wirelength is directly proportional to layout area due to minimum wire spacing design rules. The traditional minimum-cut objective is natural for this application: if the layout area is divided into a dense uniform grid, total wirelength can be expressed in "grid" units or equivalently as the sum over all gridlines of the number of wires crossing each gridline. This view can also improve auto-routability since it suggests reducing the wire congestion in any given layout region.

All of these considerations motivate the development of netlist partitioning tools that identify interconnection and communication structure in a given system design. Indeed, one of the five-year predictions issued by participants at the 1991 CANDE workshop [142] was that stand-alone partitioning for every phase of system synthesis would comprise the next major class of CAD tools to emerge in the marketplace. That this prediction has come to pass is evident from the various new tools and startup companies which focus almost exclusively on partitioning.<sup>1</sup>

Today, leading applications of partitioning include:

• General design packaging. Logic must often be partitioned into clusters, subject to constraints

<sup>&</sup>lt;sup>1</sup>Two notable examples are: High Level Design Systems, whose "advanced design planner" performs design planning at the floorplan level, and ACEO, whose "SoftWire" tool performs communication-based partitioning of multiple-FPGA systems. Partitioning is also at the heart of new tools for system-level design optimization and mapping of designs onto emulation or prototyping architectures composed of multiple field-programmable gate arrays (FPGAs).

on cluster area as well as possible I/O bounds. This problem is known as design packaging and is still the canonical partitioning application; it arises not only in chip floorplanning and placement, but also at all other levels of the system design.<sup>2</sup> The design packaging problem also arises whenever technology improves and existing designs must be repackaged onto higher-capacity modules ("technology migration"). Note that the problem is usually associated with large cluster sizes, with few constraints on the internal structure of the clusters. When a finite library of available module types is specified, the optimization is more along the lines of "covering" or "technology mapping".

- Netlist-level partitioning in HDL-based synthesis. Synthesis tools have emerged which reduce the design cycle by automatically mapping a high-level functional description to a gate-or cell-level netlist. However, even with increased maturity of such high-level synthesis tools, netlist partitioning remains central to the success of the design procedure. This is essentially because writing HDL code as opposed to performing layout can abstract away the physical layout effects of design choices (for example, a few lines of HDL code that specify a register file or crossbar connection can correspond to a large portion of the final layout area). As a result, the block decomposition of the functional (software) description does not necessarily map well into a decomposition of the physical layout. Hence, in contrast to previous building-block methodologies which yielded a small number of function blocks that could be optimally hand-partitioned, HDL-based synthesis virtually requires the physical design methodology to shift from working with a small number of building blocks to working with large, flattened design representations [53]. Partitioning of flattened inputs is also necessary for such applications as the design of "precursor systems" (i.e., finding the packaging tradeoffs that correspond to optimum cost-performance points at early stages in the product life cycle).

- Estimation for design optimization. Accurate estimation of layout area and wireability has always been a critical element of high-level synthesis and floorplanning. Now, such estimates are becoming critical to higher-level searches over the system design space. Predictive models often combine analysis of the netlist partitioning structure with analysis of the output characteristics of placement and routing algorithms, in order to yield estimates of wiring requirements and system performance. This use of system partitioning hierarchies is increasingly prominent as "design optimization" and "electronic system design automation" capture the attention of CAD users and vendors.

- System emulation and rapid prototyping (FPGA partitioning). Many logic emulation

<sup>&</sup>lt;sup>2</sup>Despite the existence of partitioning applications throughout the system design cycle, calls for papers of major CAD conferences still implicitly classify partitioning within placement and/or floorplanning. Interestingly, research activity in "pure partitioning" arguably exceeds that in either of these mainstay categories.

systems and rapid system prototyping methodologies (e.g., those from Quickturn or Zycad/Inca) use partitioning tools to map complex circuit designs onto hundreds or even thousands of interconnected FPGAs. Typically, such partitioning instances are challenging because the timing, area, and I/O resource utilizations must satisfy hard device-specific constraints. Furthermore, the partitioning optimization is affected by the discrete nature of system resources – e.g., interconnect delay in routing segments, layout area in configurable logic blocks (CLBs), or individual FPGA chips in a multiple-FPGA system – all of which have large "quanta".

• Hardware simulation and test. A good partitioning will minimize the number of inter-block signals that must be multiplexed onto the bus architecture of a hardware simulator or mapped to the global interconnect architecture of a hardware emulator. Reducing the number of inputs to a block often reduces the number of test vectors needed to exercise the logic.

In this work, we survey the major research directions in netlist partitioning and establish a taxonomy of existing works based on the underlying solution methodology. While we have tried to make this survey both complete and self-contained, we emphasize more recent problem formulations and solution approaches, possibly at the expense of methods that have been treated in previous surveys.<sup>3</sup> Section 2 develops notation, discusses various graph and hypergraph representations of the circuit netlist, and formulates basic variants of the partitioning problem. These problem formulations include bipartitioning, multi-way partitioning, constraint-driven partitioning, and partitioning with replication. Sections 3 through 6 survey four major categories of partitioning approaches:

- Section 3 discusses move-based approaches: we classify an algorithm in this category if it explores the solution space by moving from one solution to another. Greedy and iterative exchange [117] approaches are most common these always try to make the best move, but can easily can trapped in local minima. To avoid this behavior, many other strategies have been proposed including stochastic hill-climbing (simulated annealing), evolutionary algorithms, and the multistart strategy. We discuss these approaches along with many adaptations that have used these methods to address more complex formulations.

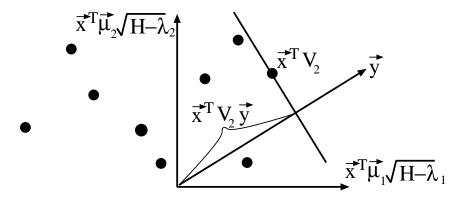

- Section 4 discusses methods that construct a **geometric representation** of the partitioning problem via such constructions as a 1-dimensional linear ordering or a multi-dimensional vector space. Such a representation offers possibilities for geometric approaches to solve problems that are intractable for general graphs. *Spectral* methods are commonly used to construct geometric representations, due to their ability to capture global netlist information.

<sup>&</sup>lt;sup>3</sup>Limited surveys are given in the textbooks [149] and [171]; the former contains a more personal perspective on early works, by W. Donath. The book by Lengauer [133] is noteworthy, especially for its complete development of combinatorial algorithms (network flow, multicommodity flow, etc.).

- Section 5 discusses **combinatorial** approaches; we loosely classify an approach under this category if the partitioning problem can be transformed into some other "classic" type of optimization, e.g., maximum flow, mathematical programming, graph labeling, or set covering. These approaches are promising since complex formulations that include timing, module preassignment, replication, and other hard constraints can often readily be expressed in terms of a mathematical program or flow network. In addition, changing user requirements for solution quality and runtime, as well as improved computing platforms, have made such approaches more practical.

- Section 6 treats **clustering**-based approaches, which traditionally consist of bottom-up approaches that merge netlist modules into small clusters. We augment this class to include methods which use a clustering solution within another algorithm, such as two-phase partitioning or placement. Clustering-based approaches have received much recent attention since they are viewed as the most promising method for tackling the increasing problem sizes in VLSI CAD.

Section 7 concludes with a discussion of benchmarking practice, as well as a brief list of perspectives on future research in the field.

# 2 Partitioning Formulations

In this section, we describe the major variant formulations of the partitioning problem. We defer the description of several less well-studied variants – e.g., retiming formulations – to the discussions of their respective underlying solution strategies.

## 2.1 Preliminaries

Given a set of n netlist modules  $V = \{v_1, v_2, \ldots, v_n\}$ , the purpose of partitioning is to assign the modules to a specified number k of clusters satisfying prescribed properties.<sup>4</sup>

**Definition:** A k-way partitioning  $P^k = \{C_1, C_2, \dots, C_k\}$  consists of k clusters (subsets of V),  $C_1, C_2, \dots, C_k$ , such that  $C_1 \cup C_2 \cup \dots C_k = V$ . If k = 2, we refer to  $P^2$  as a bipartitioning.

The objective to be optimized is denoted by  $F(P^k)$ , i.e., the objective is a function of the partitioning solution. We generally make the traditional assumption that the clusters are mutually disjoint; note however that replication formulations permit a module to be a member of more than one cluster.

<sup>&</sup>lt;sup>4</sup>Many works distinguish between the partitioning problem where k is small (e.g.,  $k \le 15$ ) and the clustering problem where k is large (e.g.,  $k = \Theta(n)$ ). Such works may refer to what we call as cluster as a "partition"; we choose not to make this distinction, since our multi-way partitioning formulations are independent of the relative size of k. For reasons of clarity, we will generally refer to  $P^k$  as a "partitioning" for small k and as a "clustering" for large k.

The most common method for representing the circuit netlist connections is as a hypergraph H(V,E) with  $E=\{e_1,e_2,\ldots,e_m\}$  being the set of signal nets (see, e.g., [23] for basic concepts of graphs and hypergraphs). Each net is a subset of V containing the modules that that net connects, and we assume that for each  $e \in E$ ,  $|e| \ge 2$ . The equivalence between netlists and hypergraphs is exact if each net has at most one pin on any module. The modules in e may also be called the pins of e. We also assume a weighting function  $w:V\to\Re$ , generally used for the area of each module. The weighting function can be extended to clusters, i.e.,  $w(C)=\sum_{v\in C}w(v)$ . Another weighting function  $w':E\to\Re$  can be defined for nets (e.g., to give higher weights for critical nets or input-output paths), but for ease of presentation we omit net-weighting from our discussion.<sup>5</sup>

**Definition:** For each module v, the set of nets incident to v is denoted by  $N(v) = \{e \in E \mid v \in e\}$  and the set of modules that are neighbors of v is denoted by  $M(v) = \{w \in V \mid \exists e \ v, w \in e, v \neq w\}$ . We say that deg(v) = |N(v)| is the degree of v, and  $deg_{min} = \min_{v \in V} deg(v)$  and  $deg_{max} = \max_{v \in V} deg(v)$  are respectively the minimum and maximum degrees of the hypergraph.

**Definition:** Each signal net e consists of a single source module S(e) and a set of destination modules D(e) (so  $\{S(e)\} \cup D(e) = e$ ), which indicates the direction of signal flow.

Many algorithms either ignore source and destination information or assume it is not available.

**Definition:** The set of hyperedges cut by a cluster C is given by  $E(C) = \{e \in E \text{ s.t. } 0 < | e \cap C | < | e | \}$ , i.e.,  $e \in E(C)$  if at least one, but not all, of the pins of e are in C. The set of nets cut by a partitioning solution  $P^k$  can be expressed as  $E(P^k) = \bigcup_{h=1}^k E(C_i)$  or equivalently  $E(P^k) = \{e \in E \mid \exists u, v \in e, h \neq l \text{ with } u \in C_h \text{ and } v \in C_l\}$ . We say that  $|E(P^k)|$  is the cut size of  $P^k$ .

Sometimes, it may be easier to represent a partitioning solution in terms of vectors and matrices, hence our final definition:

**Definition:** Given  $P^k$ , the *indicator vector* for cluster  $C_h$  is the *n*-dimensional vector  $\vec{X}_h = (x_{ih})$  with  $x_{ih} = 1$  if  $v_i \in C_h$  and  $x_{ih} = 0$  if  $v_i \notin C_h$ . The  $n \times k$  matrix X with column h equal to  $\vec{X}_h$  is the assignment matrix for  $P^k$ .

When k = 2, we have  $\vec{X}_1 = \vec{1} - \vec{X}_2$ , so only one indicator vector is needed. For this case, we let  $\vec{x} = \vec{X}_2$  represent the bipartitioning solution.

<sup>&</sup>lt;sup>5</sup>Useful information regarding the subcircuit function and the design hierarchy may be inferred from the module uniquenesses (module ID's), depending on how other development tools represent and output intermediate design representations. Current works in partitioning do not assume the availability of such information, but this may change in light of new applications such as functional clustering.

# 2.2 Circuit Representations

The choice of netlist representation is typically a consequence of the objective or the algorithmic approach, e.g., minimizing cut nets implicitly requires a hypergraph representation, and a maximum-flow solution for replication cut will require a directed network (graph) representation. Aside from the hypergraph model discussed above, standard netlist representations include:

• Weighted Undirected Graph. A graph G=(V,E) is a special case of a hypergraph with all  $|e_i| \equiv 2$ . When certain standard matrix computations or algorithm implementations are used (e.g., spectral computations or mathematical programming), an undirected graph representation is often convenient. The netlist is represented by a symmetric  $n \times n$  adjacency matrix  $A=(a_{ij})$  in which the matrix entry  $a_{ij} \geq 0$  captures the connectivity between modules  $v_i$  and  $v_j$  (so  $a_{ii} \equiv 0$  is typically assumed). Generally, for the adjacency matrix is useful only when it is sparse, i.e.,  $a_{ij} > 0$  for a very small percentage of the matrix entries.

To construct a graph from a netlist, the *clique* net model is often used: a signal net e contains |e| pins and will induce an edge between every pair of its pins; each edge has a weight that is a function of |e| (multiple edges with total weight W connecting a pair of modules are contracted into a single edge with weight W). The "standard" clique net model [133] assigns uniform weight  $\frac{1}{|e|-1}$  to each clique edge, although many other weighting functions have been proposed. It has been noted that the clique net model may enable a "finer-grain optimization" than the hypergraph

<sup>&</sup>lt;sup>6</sup>Ideally, no matter how modules of the clique are partitioned, the cost should be one, corresponding to a single cut of a net. Ihler et al. [106] prove that such a "perfect" clique net model is impossible to achieve. In addition, Lengauer [133] shows that no matter what weighting function is used, there exists a bipartitioning with deviation  $\Omega(\sqrt{|e|})$  from the desired cost of cutting a single net. The standard clique model ensures that for every signal net cut in a partitioning solution, the total weight of cut edges for that net will be at least one. However, since a cut net can contribute up to  $\frac{|e|^2}{4} \cdot \frac{1}{(|e|-1)}$  to the partitioning objective, large nets are less likely to be cut than smaller nets. A weight of  $\frac{4}{|e|(|e|-1)}$  was proposed by D. J.-H. Huang and adopted by [3] so that the expected weight of a cut signal net would be one. Hadley et al. [79] propose a weighting scheme that is a function of both |e| and k which guarantees that for the cost of splitting e into k clusters will be bounded above by one. For the maximum cost of a net cut in the transformed graph to be one, Donath [58] shows that the appropriate edge weighting is  $\frac{4}{|e|^2 - (|e| \mod 2)}$  since there are  $\frac{|e|^2 - (|e| \mod 2)}{4}$  edges crossing between two clusters when half the modules of e are in each cluster (also see [184]). Donath further shows that when there are more than two clusters,  $\frac{4}{|e|^2 - (|e| \mod 2)}$  remains the correct uniform weighting to achieve this upper bound. Many other net models are motivated by 1- and 2-dimensional cell placement. For example, the standard  $\frac{1}{|e|-1}$  weight is inspired by linear placement into fixed slots separated by distance one [40]: since the minimum wirelength of a |e|-pin net must be at least |e|-1, the weighting should be inversely proportional to |e|-1 so that the objective does not "try too hard" to place the modules into an impossibly small span of slots (also see [81]). If the span of a net is exactly |e|-1, then D. J.-H. Huang showed that a weighting function of  $\frac{6}{|e|(|e|+1)}$  gives the total wirelength |e|-1 for the clique representation. In a 2-dimensional layout, [91] assumes that the net will be a spanning tree with |e|-1 edges; hence, if the weight for these edges is evenly distributed among the clique edges, the weight function should be  $(|e|-1)/\binom{|e|}{2} = \frac{2}{|e|}$ . Frankle and Karp [68] proposed the uniform weight  $(\frac{2}{|e|})^{\frac{3}{2}}$  for linear placement with minimum squared wirelength: if the span of a net is normalized to one and edges have weight w, the total edge cost may vary from  $\frac{|e|}{2} \cdot w$  to  $(\frac{|e|}{2})^2 \cdot w$  depending on the distribution of pins; thus, Frankle and Karp set  $w=(\frac{2}{|e|})^{\frac{3}{2}}$  to minimize the worst-case deviation of cost from the square of the span (this model has also been used by [37]). Tsay and Kuh [183] propose edge weight  $\frac{2}{|e|}$  for minimizing squared wirelength and  $(\frac{2}{|e|})^3$  for minimizing Manhattan wirelength.

model, e.g., Shih [172] reports that solution quality of Fiduccia-Mattheyses bipartitioning [65] can improve when run on the graph representation of the netlist instead of the original hypergraph. However, the clique model can destroy the natural sparsity of the netlist since  $\binom{|e|}{2}$  nonzeros will be inserted in A for every net e. For example, a 1000-pin clock net will induce 499,500 nonzero entries in A. Thus, some existing methods discard large nets to maintain sparsity [37] [79]. An undirected graph can also be induced from a netlist by constructing random spanning trees, paths, or cycles over the pins in every signal net. Alternatively, dummy modules may be inserted [106], e.g., the "star" model adds a dummy node for each net and connects every pin of the net to this dummy node (cf. the discussion of [99] in Section 5.2).

- Intersection Graph: One can view the netlist partitioning problem in terms of partitioning nets instead of modules. Given such a perspective, a useful netlist representation is the intersection graph G'(V', E), whose vertices correspond to the signal nets of the original netlist hypergraph, i.e., V' ≡ {e<sub>1</sub>, e<sub>2</sub>,..., e<sub>m</sub>}. Two vertices e<sub>i</sub>, e<sub>j</sub> ∈ V' are adjacent if and only if e<sub>i</sub> ∩ e<sub>j</sub> ≠ ∅, i.e., the nets share a module. Early uses of this representation were in both partitioning [112] and placement [146]. Note that the intersection graph is typically quite sparse due to module fanout limits [80].

- Dual Hypergraph: A slightly different net-oriented representation is the dual hypergraph H(V', E'), which has the same vertex set V' ≡ {e<sub>1</sub>, e<sub>2</sub>,..., e<sub>m</sub>} as the intersection graph. However, the connections are slightly different in that modules are mapped to hyperedges: For each v ∈ V, the hyperedge N(v) is added to E' (note |E'| = n) recall that N(v) is the set of all nets incident to v. Observe that the intersection graph can be derived by applying the clique net model to the dual hypergraph. Yeh et al. [194] used this representation for their Primal-Dual FM based algorithm (see Section 3.5), and [49] used a combination of the intersection and dual representations.

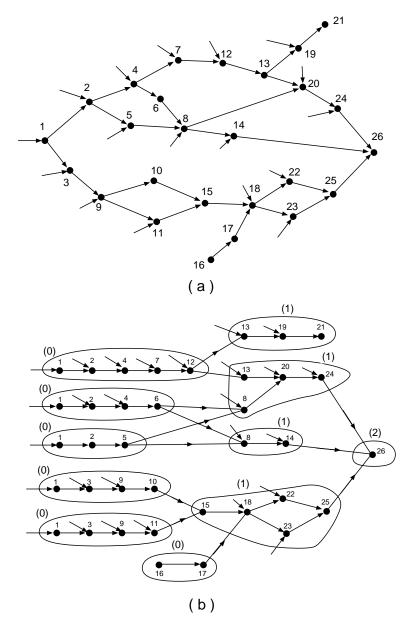

- Directed Graph: Signal flow direction can be directly integrated into a graph representation, e.g., by creating directed edges (S(e), w) for every e ∈ E and every w ∈ D(e). This specific construction is called the directed tree representation. A directed graph is particularly useful for flow, uni-directional cut, timing, and replication formulations. Sometimes this construction yields a directed acyclic graph (DAG), e.g., for combinational logic networks [50] [107]. in such a case, the set of primary inputs is denoted by PI = {v ∈ V | ∀ e ∈ N(v), S(e) = v} and the set of primary outputs is denoted by PO = {v ∈ V | ∀ e ∈ N(v), S(e) = v}.

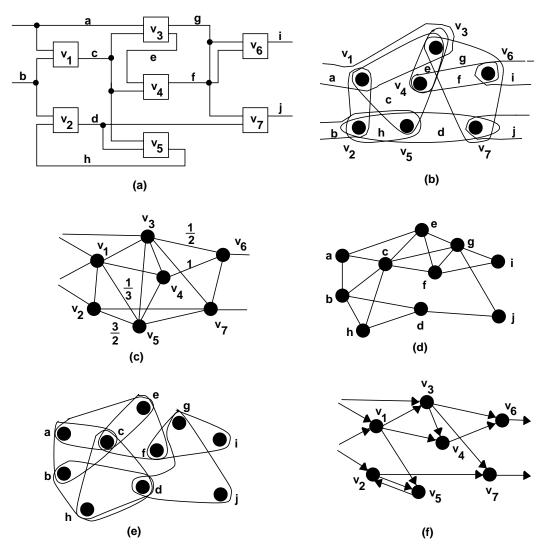

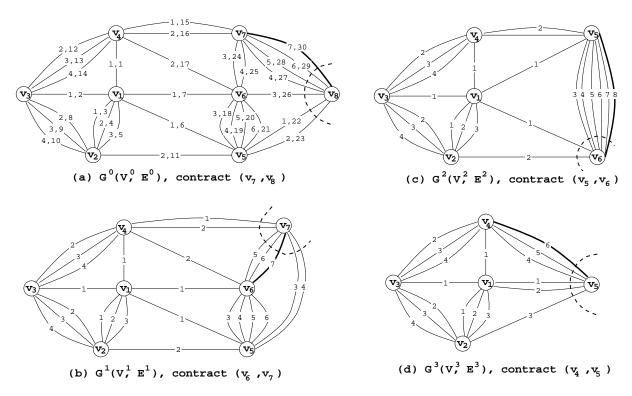

These five models are illustrated in Figure 1. In the remainder of the discussion, we will assume that the circuit is represented as a hypergraph. Of course, any method for hypergraph partitioning

can be also applied to the graph representation, as well as to the intersection and dual representations if a scheme is provided to transform the resulting net partitioning into a module partitioning.

Figure 1: Representations of a circuit with 7 modules and 10 signal nets: (a) circuit diagram with all inputs on the left side of the modules and all outputs on the right side; (b) the hypergraph representation; (c) the weighted graph representation using the standard clique net model with uniform edge weight  $\frac{1}{|e|-1}$  (only some edge weights are shown); (d) the intersection graph; (e) the dual graph; and (f) the directed graph (assuming a directed-tree hyperedge model). To enhance readability, not all edges have been labeled.

# 2.3 Bipartitioning Formulations

The min-cut bipartitioning problem seeks to divide V into two clusters such that the number of hyperedges cut by the clusters is minimized:

Min-Cut Bipartitioning: Minimize  $F(P^2) = |E(C_1)| = |E(C_2)|$  such that  $C_1 \neq \emptyset$ ,  $C_2 \neq \emptyset$ .

Min-Cut Bipartitioning can be solved by converting the hypergraph to a flow network, computing a certain set of n-1 flows and applying the max-flow min-cut theorem [66] to obtain a minimum cut. Many algorithms are known which can solve the max-flow problem in polynomial time; see [75] [2] for surveys. Note however that finding a minimum cut does not necessarily require a maximum flow; fast techniques to find minimum cuts [92] [114] [141] are noted in Section 5 below.

Optimal solutions to Min-Cut Bipartitioning will often be quite unbalanced and are thus not useful within a hierarchical design methodology; however, these solutions may form the basis of a useful heuristic [190] [191]. A more practical formulation seeks minimum-cut bipartitionings with bounds on module cardinality or total module area within each cluster. The *Min-Cut Bisection* problem seeks two equal-weight clusters:

Min-Cut Bisection: Minimize

$$F(P^2) = |E(C_1)|$$

such that  $|w(C_1) - w(C_2)| \le \epsilon$ .

If all modules have unit weight, then  $\epsilon = 1$ . When move-based heuristics are applied, it is usually convenient to allow the cluster weight imbalance  $\epsilon$  to vary up to the largest module weight (otherwise the number of possible moves may become too limited). Min-Cut Bisection is NP-complete [70], as are all of the other size-constrained formulations that we discuss since they reduce to Min-Cut Bisection.

This formulation may be unnecessarily restrictive, and relaxing the size constraints may permit a much better solution while still maintaining relatively balanced clusters.

Size-Constrained Min-Cut Bipartitioning: Given prescribed lower and upper cluster size lower and upper bounds L and U, minimize  $F(P^2) = |E(C_1)|$  such that  $L \leq w(C_h) \leq U$  for h = 1, 2.

This formulation has become popular in the recent literature, both for its greater practical relevance and as an added basis for algorithm comparisons, e.g., [156] [190] present results using unit module areas and  $L = \frac{9n}{20}$ ,  $U = \frac{11n}{20}$ , and [188] [84] present results using actual module areas and  $L = \frac{1}{4} \sum_{i} w(v_i)$ ,  $U = \frac{3}{4} \sum_{i} w(v_i)$  (see Section 7).

Rather than minimizing cutsize subject to cluster size constraints, the cutsize and balance criteria can be smoothly intergrated into the partitioning objective. The concept of ratio cut partitioning was introduced in [132] and first applied to circuit partitioning by Wei and Cheng [187].

Minimum Ratio Cut Bipartitioning: Minimize

$$F(P^2) = \frac{|E(C_1)|}{w(C_1) \cdot w(C_2)}$$

.

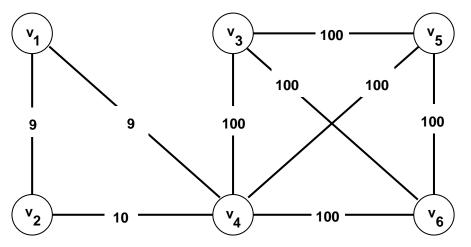

The numerator favors a low cutsize while the denominator favors more balanced cluster sizes. Figure 2 contrasts the optimal solutions for the Min-Cut Bipartitioning, Min-Cut Bisection and Minimum Ratio Cut Bipartitioning objectives.

Figure 2: Optimal bipartitionings of an edge-weighted graph with six modules. The min-cut bipartitioning  $\{\{v_1\}, \{v_2, v_3, v_4, v_5, v_6\}\}$  will have cutsize 18, but is very unbalanced. The min-cut bisection  $\{\{v_1, v_2, v_4\}, \{v_3, v_5, v_6\}\}$  has cutsize 300, much worse than the arguably more natural solution  $\{\{v_1, v_2\}, \{v_3, v_4, v_5, v_6\}\}$  which has cutsize 19 and corresponds to the optimal ratio cut of  $\frac{19}{8}$ .

# 2.4 Multi-Way Partitioning Formulations

A multi-way partitioning is a k-way partitioning with k > 2. A standard formulation is:

Min-Cut k-Way Partitioning: Given lower and upper cluster size bounds L and U, minimize  $F(P^k) = \sum_{h=1}^k E(C_h)$  such that  $L \leq w(C_i) \leq U$  for all h = 1, ..., k.

Exact cluster size balance is achieved by setting  $L = \frac{1}{k} \sum_i w(v_i) - \epsilon$  and  $U = \frac{1}{k} \sum_i w(v_i) + \epsilon$ , where  $\epsilon > 0$  may again be required for move-based algorithms to maintain feasible solutions. A similar constrained formulation used by, e.g., [18] requires that  $w(C_h) = m_h$  for user-prescribed cluster sizes  $m_1 \geq m_2 \geq \ldots \geq m_k$ . Notice that the Min-Cut k-Way Partitioning objective sums the nets cut by each cluster: a net that is cut by h clusters is counted h times in the sum. As noted by [159] [179], this objective is preferable to simply counting the number of nets cut (i.e.,  $F(P^k) = |E(P^k)|$ ) since signal nets that span more clusters can consume more I/O and timing resources. Note that the two objectives are identical for undirected graphs (which have |e| = 2 for all  $e \in E$ ).

As with bipartitioning, it is possible to integrate cutsize and cluster size balance within a single objective. To this end, Chan et al. [37] and Yeh et al. [193] respectively proposed the *Minimum Scaled Cost* and *Minimum Cluster Ratio* objectives.

Minimum Scaled Cost: Minimize

$$F(P^k) = \frac{1}{n(k-1)} \sum_{h=1}^k \frac{|E(C_h)|}{w(C_h)}.$$

Minimum Cluster Ratio: Minimize

$$F(P^k) = \frac{|E(P^k)|}{\sum_{h=1}^{k-1} \sum_{l=i+1}^{k} w(C_h) \cdot w(C_l)}.$$

Both of these objectives are k-way generalizations of the ratio cut objective, and are exactly equivalent to Minimum Ratio Cut Bipartitioning when k=2. Scaled Cost seems more useful since it penalizes nets that are divided among more than two clusters; Cluster Ratio is also more difficult to evaluate, and the  $O(k^2)$  terms in the denominator do not give immediate intuition regarding the cutsize-balance tradeoff.

Other k-way partitioning objectives have been proposed in the context of circuit clustering, i.e., when k is large with respect to |V| (see Section 6). The DS objective [48] is:

DS: Maximize

$$F(P^k) = \frac{1}{n} \sum_{h=1}^{k} \frac{degree(C_h)}{separation(C_h)}$$

where  $degree(C_h)$  is the average number of nets incident to each module of the cluster that have at least two pins in the cluster, and  $separation(C_h)$  is the average length of a shortest path between two modules in  $C_h$  (=  $\infty$  if the cluster is disconnected). Since DS requires  $O(n^3)$  time to evaluate, it is more useful for comparison rather than optimization of clustering solutions.

The Absorption objective [179] measures the sum of the fractions of nets "absorbed" by the clusters:

Absorption: Maximize

$$F(P^k) = \sum_{h=1}^k \sum_{e \in E \mid e \cap C_h \neq \emptyset} \frac{|e \cap C_h| - 1}{|e| - 1}$$

e.g., net e incident to cluster  $C_h$  adds absorption zero if e has only one pin in  $C_h$ , and adds absorption one if all of e's pins are in  $C_h$ .

The *Density* objective [101] maximizes the sum of cluster *densities*, where the density of a cluster C is the number of hyperedges completely contained in C, divided by the the weight of C:

**Density:** Maximize

$$F(P^k) = \sum_{h=1}^k \frac{|\{e \in E \mid e \subseteq C_h\}|}{w(C_h)}$$

Density differs from Absorption in that only nets completely absorbed in the cluster are counted. Without this denominator, the objective is equivalent to minimizing the total number of cut nets (cf. the "Clustering" problem in [133]), since it can be rewritten as  $E - E(P^k)$ .

A very important clustering-related formulation captures the problem of timing-driven k-way partitioning (see Section 5.1 below). A DAG representation is assumed, and we seek to minimize the longest delay over all paths from primary inputs to primary outputs of the circuit, subject to satisfying the size constraint  $w(C) \leq U$ . Each module  $v \in V$  has delay  $\delta(v)$ , and an edge  $(v_i, v_j)$  between two modules has delay one if  $v_i$  and  $v_j$  are in different clusters, and delay zero if  $v_i$  and  $v_j$  are in the same cluster. In other words, the cost(delay) of a path p from  $v_i$  to  $v_j$  can be written as  $cost(p) = \sum_{v \in p} \delta(v) + K(p)$ , where K(p) is the number of intercluster edges in p.

Min-Delay Clustering: Given a DAG G(V, E), module delays  $\delta(v_i)$  and cluster size bound U, minimize  $F(P^k) = \max_{\text{all paths } p} cost(p)$  such that  $w(C_h) \leq U$  for all  $h = 1, \ldots, k$ .

As noted in [151], this formulation can capture delay between adjacent modules  $v_i$  and  $v_j$  by inserting a dummy module  $v_m$  on edge  $(v_i, v_j)$  with  $w(v_m) = 0$  and edge delay  $\delta(v_m)$ ; such a transformation only increases the size of the netlist by a constant factor. Applications of Min-Delay Clustering abound in the performance-driven design of multi-chip module (MCM) or multiple-FPGA systems. For example, in the latter application a technology-mapped circuit will have been decomposed into configurable logic block (CLB) equivalents, and these must be partitioned onto k FPGA devices subject to hard I/O limits for each device.

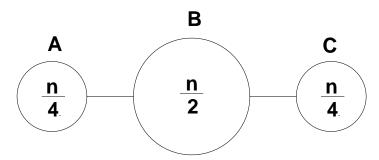

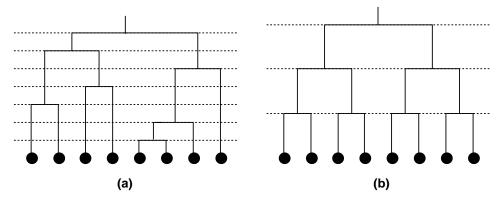

Finally, there is the class of layout-driven multi-way partitioning formulations, which are generally motivated by the link between partitioning and placement in typical physical design methodologies. Vijayan [186] proposed an abstract formulation that requires the netlist modules to be mapped onto an underlying k-node tree structure. Each node of the tree has a prescribed capacity of netlist modules, and the cost of the k-way partitioning is the sum of the costs of routing each net on the underlying tree structure. Thus, a tree consisting of two nodes, each with capacity  $\frac{n}{2}$ , captures Min-Cut Bisection. Similarly, a star topology with k leaf nodes each having capacity  $\frac{n}{k}$ , along with a dummy central vertex having zero capacity, captures balanced Min-Cut k-Way Partitioning. Vijayan notes many applications of his formulation, including seeding of functional blocks, partitioning within nonrectangular regions, and residual logic partitioning.

For layout-driven applications, a general graph topology rather than a tree structure can better incorporate information about the layout geometry [182]. For example, if modules are assigned to 12 identical devices that are arranged in a  $3 \times 4$  grid, the cost of a cut net might correspond to the routing tree cost over the devices that contain pins of the net. This formulation applies to partitioning for multiple-FPGA systems, MCM designs, and general floorplanning. As with Vijayan's formulation, edge-weighting of the underlying topology can be used to model distance, signal delay, routing congestion or other layout parameters. Roy and Sechen [159] have integrated both the perimeter of a net's bounding box and penalties for wirelength of critical-paths into an objective function for MCM

partitioning. Similar formulations are given in [158] [171]. The quadrisection problem [178] is a classic special case of the same formulation for standard-cell placement: the underlying graph is a  $2 \times 2$  grid, and the objective is to minimize the number of nets crossing the horizontal and vertical middle gridlines.

# 2.5 Constraint-Driven (Satisficing) Formulations

With the increasing complexity of system design, CAD optimizations are becoming constraint-driven, i.e., satisficing, meaning that the design problem is expressible as a decision question. If the answer to the decision question is yes, then there exists a feasible solution that satisfies all the constraints, and all feasible solutions are equally good. For example, a design that can achieve a given system clock speed, fit into a given gate array, meet given I/O constraints on logic blocks, etc. will indeed be a good solution. Constraint-driven partitioning formulations are most prominent in the design of multiple-FPGA systems for rapid prototyping or system emulation. Because FPGA gate density is low, and because logic (CLB) and I/O resources both have hard upper bounds, FPGA partitioning is virtually a canonical constraint-driven application. Thus, we use the term "FPGA partitioning" to exemplify the more general case of partitioning with area, I/O and perhaps timing constraints. In FPGA partitioning, a cluster corresponds to an FPGA device (i.e., a chip), so that the circuitry of the modules and the connections in the cluster must be mappable onto the chip. If all the devices are of the same type, Kužnar et al. [125] proposes finding a feasible solution that minimizes the number of devices.

**Definition:** A cluster C is feasible with respect to FPGA device type D if  $w(C) \leq w(D)$  and  $E(C) \leq E(D)$  where w(D) is the capacity and E(D) is the I/O limit of the device type D.

Single-Device FPGA Partitioning: Given an FPGA device type D, find  $P^k = \{C_1, C_2, \dots C_k\}$  such that every  $C_k \in P^k$  is feasible with respect to D and  $F(P^k) = k$  is minimized.

This formulation has also been studied in, e.g., [44] [100]. Notice that this formulation is easily stated as a decision question – "Given a value k and a device type D, does there exist a feasible  $P^k$  with respect to D?" More generally, a library of different device types with varying size capacities and I/O limits may be available. Each device type D has an associated cost, denoted by cost(D). Let  $\Delta = \{D_1, D_2, \ldots, D_r\}$  denote a library of devices and let  $dev : 2^V \to \Delta$  be a partial mapping of possible clusters to the lowest-cost device types for which they are feasible. The multiple-device FPGA partitioning problem [125] is:

Multiple-Device FPGA Partitioning: Given a library of devices  $\Delta$ , find  $P^k = \{C_1, C_2, \dots C_k\}$  and a partial mapping dev such that every  $C_h \in P^k$  is feasible with respect to  $dev(C_h)$  and  $F(P^k)$

$\sum_{h=1}^{k} cost(dev(C_h))$  is minimized.

For satisficing problems, it is often the case that many solutions can achieve the same cost. In practice, other criteria can be used to distinguish superior solutions. For example, if w(C) is very close to w(dev(C)), then the FPGA device may not be routable; one may seek to balance "slacks" w(dev(C)) - w(C)) among the clusters in order to yield the highest possibility of routing. As another example, it might be desirable to minimize the number of pins used,  $\sum_{i=1}^{k} |E(C_i)|$ , since this quantity represents total interconnect between FPGAs. This pin-minimization objective was proposed by Woo and Kim [189], who also studied a more rigid capacity constraint: each module has an associated "cell type" and each FPGA device can only contain a fixed number of modules of each cell type.

# 2.6 Replication Formulations

The final class of formulations that we preview removes the assumption that clusters are disjoint, i.e., a module can belong to multiple clusters [122]. Replicating modules can reduce the cutsize, and is particularly useful for FPGA partitioning since many device architectures seem more I/O-limited or interconnect-limited than logic-limited. Replication can also reduce the number of interchip wires along a given path, increasing system performance. There are three forms of replication in the literature, respectively involving directed graphs [103], hypergraphs with source and destination information [122], and functional information [126] (i.e., the actual logic functions must be known in addition to the circuit topology).

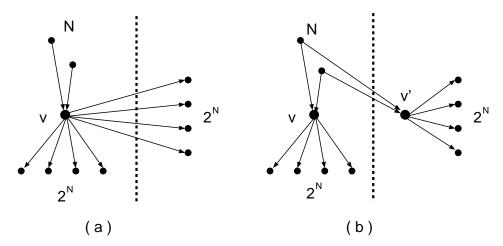

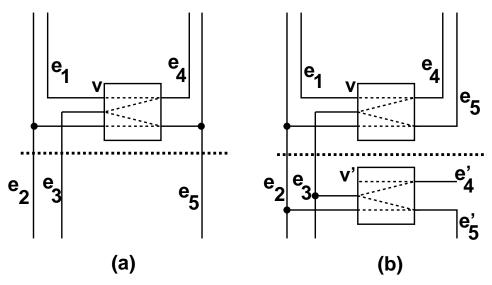

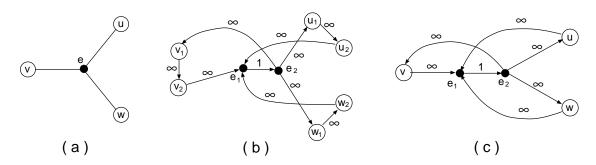

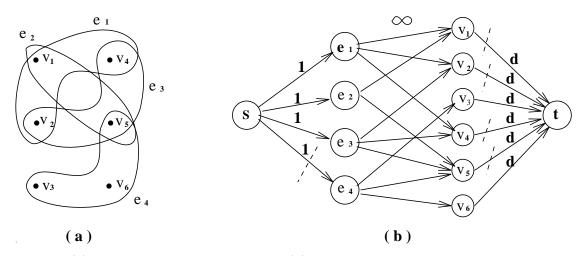

Consider the directed graph shown in Figure 3(a), in which module v represents an N-input decoder circuit. The cut shown has size  $2^N$ , but if the decoder v is replicated as in (b), every one of these  $2^N$  edges will become uncut (however, N new edges will be cut). The following rules are used to modify the edge set E when  $v \in C_h$  is replicated into  $v' \in C_l$ .

## Directed Graph Replication Rules: [103]

- For each (v, w) with  $w \in C_l$ , replace (v, w) with (v', w).

- For each  $(w, v) \in E$ , add (w, v') to E.

Notice that the  $2^N$  edges were removed in Figure 3(b) according to the first rule, and the addition of N edges followed from the second rule.

These rules can be extended to hypergraphs, where source and destination information are known [122]. The following rules are used to modify the edge set E when  $v \in C_h$  is replicated into  $v' \in C_l$ .

#### Hypergraph Replication Rules:

Figure 3: Directed graph corresponding to an N-to- $2^N$  decoder v. Replication of v reduces the cut size from  $2^N$  in (a) to N in (b).

- For every net e with v = S(e) and for every  $w \in D(e) \cap C_l$ , remove w from e; create a new net e' with S(e') = v' and  $D(e') = \{w \in D(e) \cap C_l\}$ . Delete any resulting 1-pin nets from the hypergraph.

- For every net e with  $v \in D(e)$ , add v' to D(e).

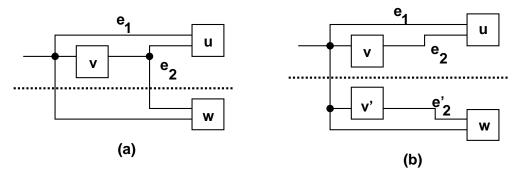

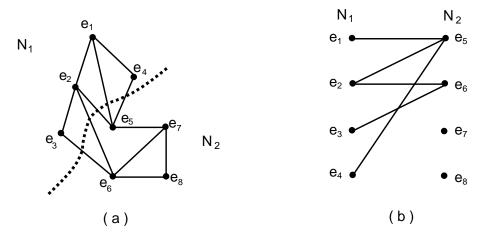

Note the difference between this second rule and the corresponding rule for directed graph replication. Figure 4 shows an example with inputs (outputs) on the left (right) side of each module. By the first rule, replicating v adds the new net  $e'_2$  containing v' and w to the set of hyperedges; by the second rule, v' is added as another destination module for net  $e_1$ . Thus,  $e_1$  is still cut only once, but if a directed tree representation and the directed graph rules were applied (as in [103]), both the edges  $(S(e_1), v')$  and  $(S(e_1), w)$  would cross the cut.

The third replication formulation is due to Kužnar et al. [126] and assumes functional knowledge of the circuit. The key idea is that if one knows the actual function of a module, then not all of the incoming signals may be required by both copies of the replicated module. The first hypergraph replication rule above is applied to construct new nets and remove any resulting 1-pin nets. Then, the second hypergraph replication rule is modified (again, when replicating v to v') to:

**Logic-Dependent Replication Rule:** Let  $E^* = \{e \mid S(e) = v'\}$ . For every net e such that  $v \in D(e)$ , if  $\exists e^* \in E^*$  that depends on e, add v' to D(e).

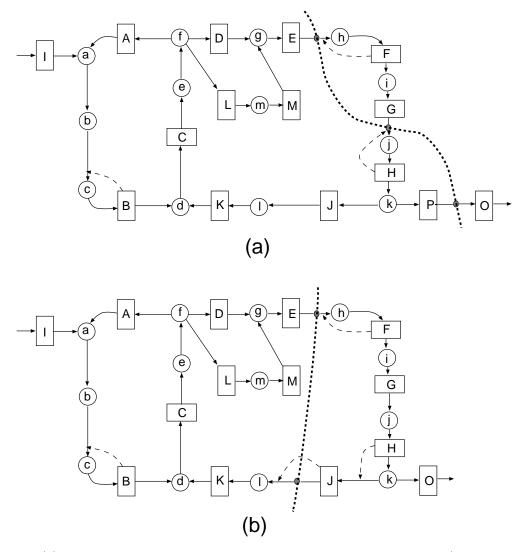

Consider the module v shown in Figure 5(a), with three inputs  $e_1$ ,  $e_2$ ,  $e_3$  and two outputs  $e_4$ ,  $e_5$ . From the dotted lines within the modules, we see that output  $e_4$  depends only on inputs  $e_1$  and  $e_3$ , while output  $e_5$  depends only on inputs  $e_2$  and  $e_3$ . Three nets cross the cutline in (a), but only two

Figure 4: (a) A circuit with two nets crossing the cut, and (b) the same circuit with module v replicated, yielding only one cut net.

nets are cut after v has been replicated to v' in (b). Applying the first replication rule deletes  $e'_4$  (since  $D(e'_4) = \emptyset$ ) while  $e'_5$  remains. Applying the second rule using  $E^* = \{e'_5\}$  shows that v' needs connections to  $e_2$  and  $e_3$  only, since  $e'_5$  does not depend on  $e_1$ . This formulation is germane to FPGA system synthesis, e.g., CLBs of such popular device families as the Xilinx 4000-series indeed have multiple outputs with differing dependencies on the input variables.

Figure 5: (a) A module v with three nets crossing the cut; (b) replication requires only two nets to cross the cut since the net corresponding to input  $e_1$  is not needed by v'.

# 3 Move-Based Approaches

A partitioning approach is move-based if it iteratively constructs a new candidate solution based on two considerations: (i) a neighborhood structure that is defined over the set of feasible solutions, and (ii) the previous history of the optimization. The first consideration requires the notion of a local perturbation of the current solution; this is the heart of the move-based paradigm. The type of perturbation used determines a topology over the solution space, known as the neighborhood structure. For the objective function to be "smooth" over the neighborhood structure, the perturbation (also known as a neighborhood operator) should be small and "local". Typical neighborhood operators for partitioning include swapping a pair of modules, or shifting a single module, across a cluster boundary. For example, two partitioning solutions are neighbors under the pair-swap neighborhood structure if one solution can be derived from the other by swapping two modules between clusters. In general, the solution space is explored by repeatedly moving from the current solution to a neighboring solution. With respect to previous history, some approaches are "memoryless", e.g., a simple greedy method might rely only on the current solution to generate the next solution. On the other hand, such methods as Kernighan-Lin or Fiduccia-Mattheyses implicitly remember the entire history of a "pass"; hybrid genetic-local search or tabu search approaches must also remember lists of previously seen solutions.

Move-based approaches dominate both the literature and industry practice for several reasons. First, they are generally very intuitive – the logical way of improving a given solution is to repeatedly make it better via small changes, such as moving individual modules. Second, iterative algorithms are simple to describe and implement; for this reason, the bipartitioning method of Fiduccia-Mattheyses [65] and the multi-way partitioning method of Sanchis [164] are standards against which nearly all other heuristics are measured. Third, the move-based approach encompasses more sophisticated strategies for exploring the solution space – e.g., simulated annealing, tabu search, and genetic algorithms – which yield performance improvements over greedy iterative methods while retaining the intuitiveness associated with local search. Finally, the move-based approach is independent of the nature of the objective function that is used to measure solution quality. While other approaches might require the objective to be of a particular form, or a relatively simple function of solution parameters, the move-based approach can flexibly incorporate arbitrary constraints (e.g., on critical path delays or I/O utilization). Thus, the move-based approach has been applied to virtually every known partitioning formulation.

The remainder of this section is organized as follows. We first discuss the "classic" greedy iterative improvement algorithms, which move from the current solution to the *best* neighboring solution. We also discuss implementation issues that can greatly affect the performance of these methods. We then discuss three *stochastic hill-climbing* methods – simulated annealing, tabu search, and genetic

algorithms – which can move to higher-cost neighboring solutions in order to escape local minima. Finally, the section concludes by reviewing the numerous works that have each adapted some basic move-based paradigm in addressing some variant partitioning formulation.

## 3.1 Iterative Improvement

Iterative improvement algorithms are based on the greedy strategy: start with some feasible solution and iteratively move to the best (improving) neighboring solution. The process terminates when the algorithm reaches a local minimum, i.e., a solution for which all neighbors have greater cost. Early greedy improvement methods apply simple pair-swap or single-move neighborhood operators, and quickly reach local minima corresponding to poor solutions. By contrast, the strategies discussed in this subsection all rely on extended neighborhood structures which effectively allow hill-climbing out of local minima (even though each strategy is greedy with respect to its neighborhood operator). Due to these methods, iterative improvement remains a viable strategy, particularly when clustering techniques are integrated (see Section 6).

### 3.1.1 The Kernighan-Lin (KL) Algorithm

In 1970, Kernighan and Lin [117] introduced what is often described as the first "good" graph bisection heuristic. Their algorithm uses a pair-swap neighborhood structure and proceeds in a series of passes. During each pass of the algorithm, every module moves exactly once, either from  $C_1$  to  $C_2$  or from  $C_2$  to  $C_1$ . At the beginning of a pass, each module is unlocked, meaning that it is free to be swapped; after a module is swapped it becomes locked. KL iteratively swaps the pair of unlocked modules with the highest gain, where the gain of swapping  $v_i \in C_1$  with  $v_j \in C_2$  is given by  $F(\{C_1, C_2\}) - F(\{C_1 + v_j - v_i\}, \{C_2 + v_i - v_j\})$ . In other words, the gain is the decrease in solution cost that results from the pair-swap. For a weighted undirected graph and the min-cut objective, the gain for these modules is given by

$$gain(v_i, v_j) = \sum_{v_k \in C_2} (a_{ik} - a_{jk}) + \sum_{v_k \in C_1} (a_{jk} - a_{ik}).$$

The swapping process is iterated until all modules become locked, and the lowest-cost bisection observed during the pass is returned. Another pass is then executed using this bisection as its starting solution; the algorithm terminates when a pass fails to find a solution with lower cost than its starting solution. An advantage of KL is that it can in some sense climb out of local minima, since it always swaps the pair of modules with highest gain even if this gain is negative. However, if we consider all solutions

reachable within a single pass of the algorithm to be "neighbors" of the current solution, the KL algorithm is still seen to be greedy.

A simple implementation of KL requires  $O(n^3)$  time per pass since finding the highest-gain swap involves evaluating  $O(n^2)$  swaps. In practice, this complexity is reduced to  $O(n^2 \log n)$  by maintaining a sorted list of gains. The number of passes is clearly bounded by |E| for unweighted graphs (since the cost must improve with each pass); in practice, significantly fewer passes will be needed to reach a local minimum. Recently, Dutt [61] presented the  $Quick\ Cut$  algorithm which reduces the complexity of a single KL pass to  $O(\max\{|E| \cdot \log n, |E| \cdot deg_{max}\})$  where  $deg_{max}$  is the maximum module degree. The speedup is based on the observation that it is not necessary to search more than a certain subset of  $(deg_{max})^2$  module pairs to find the pair with highest gain. Although the original KL algorithm and Quick Cut apply only to undirected weighted graphs, Schweikert and Kernighan [169] extended KL to hypergraphs and a similar extension appears possible for Quick Cut.

#### 3.1.2 The Fiduccia-Mattheyses (FM) Algorithm

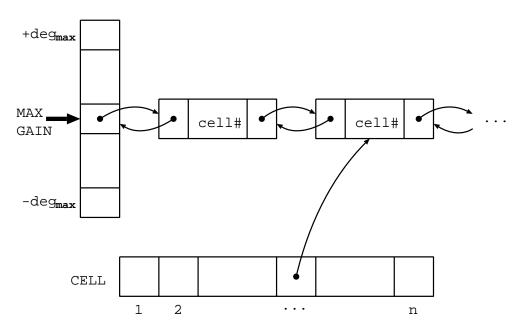

Fiduccia and Mattheyses [65] presented a KL-inspired algorithm which reduced the time per pass to linear in the size of the netlist. The main difference between KL and FM is the neighborhood structure: a new bipartitioning is derived by moving a single module either from  $C_1$  to  $C_2$  or from  $C_2$  to  $C_1$ . Since intermediate solutions considered by FM must violate the strict bisection constraint, the solution is permitted to deviate from an exact bisection by the size of the largest module. The gain associated with module  $v \in C_i$  is  $|E(C_i)| - |E(C_i - v)|$ . Like KL, the FM algorithm performs passes wherein each module moves exactly once, returns the best solution observed during a pass, and terminates when a pass fails to improve the cost function. However, FM permits a much faster O(|E|) implementation on undirected graphs and an O(p) implementation on hypergraphs, where p is the number of pins in the netlist. The key to the speedup is the pain bucket data structure shown in Figure 6, which allows constant-time selection of the module with highest gain and fast gain updates after each move.

The efficient management of gain buckets is possible because (i) all module gains are integers, and (ii) every gain is bounded above by  $deg_{max}$  and below by  $-deg_{max}$ . Even when variations of the pure min-cut objective are permitted (e.g., non-integral net weights), there is usually a tight bound on the range of possible gain values. At the beginning of a pass, the gains for each of the n possible module moves are computed in O(p) time, and each move is inserted into the data structure according to its gain. The modules with highest gain are stored in the bucket with gain value MAXGAIN. During an FM pass, a module is selected from this bucket and deleted from the linked list; the module is moved from its current cluster and the gains of unlocked modules incident to the moved module are updated. The updating of a module can be accomplished by removing it from its gain bucket list and inserting it

at the head of the bucket list indexed by its new gain value. If one of these modules has new gain that is larger than MAXGAIN, then MAXGAIN is updated to this new value. If the bucket indexed by MAXGAIN becomes empty, then MAXGAIN is decreased until it indexes a non-empty bucket.

Figure 6: The gain bucket list structure as shown in [65].

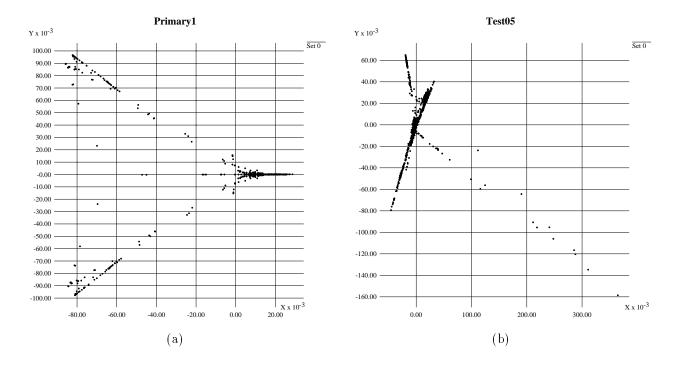

## 3.1.3 Tie-Breaking Strategies

A frequently cited enhancement to FM is that of Krishnamurthy [123]. He suggested that the lack of an "intelligent" tie-breaking mechanism from among the many possible modules in the highest-gain bucket could cause FM to make "bad" choices. Hagen et al. [86] observe that 15 to 30 modules will typically share the highest-gain value at any time during an FM pass on the Primary1 MCNC benchmark (833 modules). As a tie-breaking mechanism, Krishnamurthy introduced a gain vector, which is a sequence of potential gain values corresponding to numbers of possible moves into the future. Thus, the  $r^{th}$  entry in the gain vector looks r moves ahead, and ties are broken lexicographically by  $1^{st}$ -level gains, then  $2^{nd}$ -level gains, etc. Gain vectors can be integrated into the FM gain bucket structure, increasing the complexity to O(pr), where r is the maximum number of lookahead moves stored in the gain vector.

Krishnamurthy defines the binding number  $\beta_{C_i}(e)$  of a signal net e with respect to cluster  $C_i$  as the number of unlocked modules in  $C_i \cap e$ , unless  $C_i \cap e$  contains a locked module, in which case  $\beta_{C_i}(e) = \infty$ . Intuitively, the binding number measures how many modules must be moved from  $C_i$  in order to move all the pins in e out of  $C_i$ . This is impossible when a module in  $C_i \cap e$  is locked, so the

binding number is infinite. The  $r^{th}$ -level gain  $\gamma_r(v)$  for  $v \in C_1$  is given by

$$\gamma_r(v) = |\{e \in E(\{v\}) \text{ s.t. } \beta_{C_1}(e) = r, \beta_{C_2}(e) > 0\} |$$

$$- |\{e \in E(\{v\}) \text{ s.t. } \beta_{C_1}(e) > 0, \beta_{C_2}(e) = r - 1\} |$$

(3.1)

The first term counts how many nets with binding number r-1 are "created" by the move, and the second term counts how many nets with binding number r-1 are "destroyed" by the move (i.e., have new binding number  $=\infty$ ). Hence, the  $r^{th}$ -level gain counts the additional number of nets that may possibly become uncut following r moves. Note that the  $1^{st}$ -level gain is identical to the gain in the FM algorithm. Although the benefit of higher-level gains is well-documented (e.g., [94]), small modifications might improve performance. For example, instead of combining the positive and negative gains into a single term, once could store both terms separately to afford a two-tiered  $r^{th}$ -level comparison.

Even with Krishnamurthy's gain vector, ties may still occur in the  $1^{st}$ - through  $r^{th}$ -level gains. In this case, the implementation of the gain bucket data structure will determine which module is selected. The original FM algorithm uses a linked list for each bucket; from Figure 6, reproduced from [65], we may infer that modules are removed and inserted at the head of the list, i.e., the bucket organization corresponds to a Last-In-First-Out (LIFO) stack. The authors of [65] do not mention why a LIFO organization was chosen, but one can speculate that it was an "obvious" choice. However, a First-In-First-Out (FIFO) organization which supports the same update efficiency could also be implemented, simply by removing modules from the head of the linked list and inserting modules at the tail of the linked list. Alternatively, a random organization could be implemented, though the time complexity would increase slightly since bucket selection could not be accomplished in constant time.

Recently, the authors of [86] observed that Sanchis [164], and most likely Krishnamurthy [123] also, used random selection from gain buckets in their implementations. Furthermore, [86] observed that a LIFO gain bucket organization yields considerably superior solutions than either the FIFO or random bucket organization, for both the FM and Krishnamurthy algorithms. (This result seems quite surprising: if anything, "folklore" would have it that introducing randomness can improve solution quality by increasing the range of the neighborhood search.) One possible explanation for the success of LIFO is that it enforces "locality" in the choice of modules to move, i.e., modules that are naturally clustered together will tend to move sequentially. Hagen et al. [86] use this idea of locality to propose an alternative formula for higher-level gains which also improves performance. Given that slight modifications to the bucket organization or gain formula can so dramatically affect the solution quality obtained by these iterative approaches, exploring other implementation choices seems to be a very promising direction for future work. The importance of such research is heightened by the present widespread use of the FM and Krishnamurthy algorithms.

### 3.1.4 Sanchis' Multi-Way Partitioning Algorithm

Sanchis [164] extended the FM algorithm, together with Krishnamurthy's lookahead scheme, to multi-way partitioning. The algorithm is generally straightforward, although there are several knotty implementation issues. Sanchis' detailed explanation of these issues accounts for her algorithm's wide use in practice, as well as its present status as a benchmark against which multi-way partitioning heuristics are compared.

Sanchis extends the definition for the binding number of a net e with respect to cluster  $C_i$  as  $\beta'_{C_i}(e) = \sum_{j \neq i} \beta_{C_j}(e)$ . In other words,  $\beta'_{C_i}(e)$  is the sum of the Krishnamurthy binding numbers for e with respect to every cluster except  $C_i$ , and measures the difficulty of removing the pins in e from  $C_i$ . The analog of equation (3.1) for the  $r^{th}$ -level gain of moving module  $v \in C_i$  to  $C_j$  is

$$\gamma_{r}(v) = |\{e \in E(\{v\}) \ s.t. \ \beta'_{C_{i}}(e) = r, \beta'_{C_{i}}(e) > 0\} |$$

$$- |\{e \in E(\{v\}) \ s.t. \ \beta'_{C_{i}}(e) > 0, \beta'_{C_{i}}(e) = r - 1\} |$$

$$(3.2)$$

Equation (3.2) assumes that the objective is  $F(P^k) = |E(P^k)|$ . In [165], Sanchis shows how to modify this formula to handle the objective function which assigns cost j-1 to a net that spans j clusters (this is very similar to  $F(P^k) = \sum_{h=1}^k |E(C_h)|$ ). For this objective, the  $r^{th}$ -level gain is

$$\begin{split} \gamma_r(v) = & \quad \mid \{e \in E(\{v\}) \ s.t. \ \beta_{C_i}(e) = r, \beta_{C_j}(e) > 0\} \mid \\ & \quad - \quad \mid \{e \in E(\{v\}) \ s.t. \ \beta_{C_i}(e) > 0, \beta_{C_i}(e) = r - 1\} \mid \end{split}$$

#### 3.2 Simulated Annealing

Simulated Annealing (SA) was popularized by Kirkpatrick et al. [119] as an alternative to greedy approaches, which are quickly trapped in local minima since they can only make downhill moves. Given a neighborhood structure and a current solution, SA picks a random neighbor of the current solution and moves to this new solution if it represents a downhill move. Even if the new solution represents an uphill move, SA will move to it with probability  $e^{-\frac{\Delta}{T}}$  (termed a "Boltzmann acceptance rule") and otherwise retain the current solution; here,  $\Delta$  is the cost of the new solution minus the cost of the current solution, and T is the current value of a temperature parameter which guides the optimization. To control the rate of convergence and the strategy for exploring the solution space, the user typically establishes a temperature schedule by which T varies, e.g., as a function of the number of moves made. The SA algorithm enjoys certain theoretical attractions [72] [88] (see also [127]): using Markov chain arguments and properties of Gibbs-Boltzmann statistics, one can show that SA will converge to a globally optimum solution given an infinite number of moves and a temperature schedule that cools to zero sufficiently slowly. The use of terms such as "cooling" and "temperature schedule"

are due to SA's analogy to physical annealing of a material into a ground-state energy configuration.

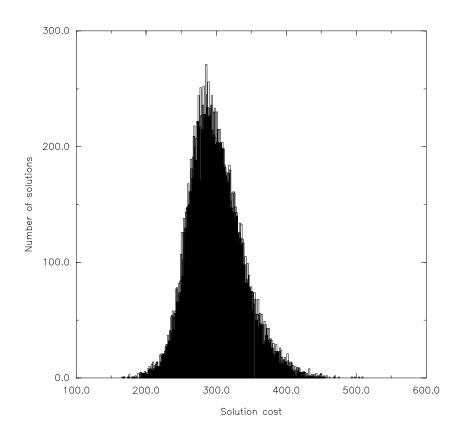

For the Min-Cut Bisection problem, Johnson et al. [110] conducted an extensive empirical study of simulated annealing versus iterative improvement approaches, using various random graphs as a testbed (see Section 7.1). The authors of [110] conclude that SA is a competitive approach, outperforming KL for uniform and geometric random graphs. However, they suggest that multiple runs of KL with random starting solutions may be preferable to SA for sparse graphs that have local structure (a description that applies to circuit netlists). They also make a number of interesting observations, including:

- Starting SA with a good solution as opposed to a random solution may be advantageous, particularly if the good solution can identify and exploit special structure of the instance.

- Spending long periods of time at high temperatures is not necessary.

- Geometric cooling schedules (i.e., setting  $T = \alpha^M T_0$  where M is the number of moves made and  $T_0$  is the initial temperature) seem at least as effective as nonadaptive alternatives such as logarithmic or linear cooling. Adaptive cooling schedules which are modified during the execution of SA (e.g., based on solution quality, distribution of solution costs in the neighborhood, etc.) hold promise.

- Expanding the feasible solution space may be worthwhile (e.g., by loosening the size constraints

for bisection); expanding the neighborhood structure allows good solutions to be found more

quickly.

These conclusions are based on studies of random graphs which do not possess natural hierarchical structure. Although there is no a priori reason to doubt such conclusions will also hold for circuit netlists, similar studies using VLSI circuits would seem worthwhile. We note that annealing is generally not yet viewed as "practical" for VLSI partitioning applications: runtimes are simply too long. For this reason, there is only limited work that addresses the use of SA for VLSI partitioning. Parallel implementations, improved temperature schedules, and two-stage approaches which anneal at low temperature starting from a good heuristic solution have all been investigated for VLSI placement, where annealing has often outperformed other heuristics. Quite possibly, such enhancements will make SA more viable for partitioning applications in the future.

One reason for long SA runtimes is that at low temperatures, many candidate moves (i.e., neighbors of the current solution) might be generated and rejected before one is finally accepted. Greene and Supowit [78] proposed a "rejectionless" variant of SA in which no moves are rejected, since candidate moves are generated with probability proportional to their likelihood of being generated and accepted given the current solution. For bipartitioning, a "gain" must be stored for each module, and only

the gains for modules in M(v) need to be updated when v is moved. The Boltzmann acceptance rule maps the gain of v to a weight w(v), and the probability that v is generated (and moved to) is  $w(v)/\sum_{u\in V} w(u)$ .

Recently, Roy and Sechen [159] used simulated annealing to implement a timing-driven MCM partitioning algorithm. Their cost function is the sum of the half-perimeters of each net spanning multiple chips on the MCM, plus a timing penalty for critical nets whose wirelength exceeds predefined constraints. Chatterjee and Hartley [41] presented an SA-based heuristic which performs partitioning and placement simultaneously. Their cost function is the sum of five components: conflict and capacity costs which combine to measure the feasibility of mapping a cluster onto the chip, a wasted space cost that penalizes unused resources on the chip, a half-perimeter net cost, and a pin cost. These works illustrate the ease with which SA can address relatively arbitrary objective functions (of course, simple objective functions are preferred since evaluation of solution cost dominates the runtime). Sun and Sechen [179] have also used SA to optimize Absorption in a clustering preprocessor within the TimberWolf placement tool.

#### Mean Field Annealing

Mean Field Annealing (MFA) is a technique similar to SA which also has a physical analogy to systems of particles in thermal equilibrium. Van den Bout and Miller [54] showed how MFA could be applied to graph partitioning. They use an indicator n-vector  $\vec{x}$  to denote a bipartitioning solution, where  $x_i = 0$  corresponds to membership of  $v_i$  in  $C_1$  and  $x_i = 1$  corresponds to membership of  $v_i$  in  $C_2$ . However,  $x_i$  can also take on any real value between 0 and 1. Initially, each  $x_i$  is set to be slightly larger than 0.5. Iteratively, a random  $v_i$  is chosen and the two solutions  $\vec{x}(0)$  with  $x_i = 0$  and  $\vec{x}(1)$  with  $x_i = 1$  are evaluated (the cost function is extended to non-discrete solutions). MFA then finds a "compromise" value for  $x_i$ ,

$$x_i = (1 + e^{(F(\vec{x}(1)) - F(\vec{x}(0)))/T})^{-1}$$

and  $\vec{x}$  is modified accordingly for the next iteration. The intuition behind this assignment is that  $x_i$  should migrate towards its natural value, e.g., if  $F(\vec{x}(1)) = F(\vec{x}(0))$  then  $x_i = 0.5$  and if  $F(\vec{x}(1)) \ll F(\vec{x}(0))$  then  $x_i \approx 1$ .

This process of choosing a random  $v_i$  and computing a new  $x_i$  value is repeated until a stable solution is reached., The temperature T is then lowered and the algorithm repeated; this polarizes the  $x_i$  values further (to 0 or 1). Finally, a graph bipartitioning solution is obtained by rounding each  $x_i$  to its nearest discrete value. Bultan and Aykanat [33] have extended this basic approach to multi-way partitioning of hypergraphs. An earlier work of Peterson and Anderson [145] studied the performance

of MFA for graph bisection; their formulation used  $\vec{x}$  with  $x_i = -1$  if  $v_i \in C_1$  and  $x_i = 1$  if  $v_i \in C_2$ , with maximization objective

$$F(\vec{x}) = \frac{1}{2} \sum_{i=1}^{n} \sum_{j=1}^{n} a_{ij} x_i x_j - \frac{\alpha}{2} (\sum_{i=1}^{n} x_i)^2$$

where  $\alpha$  is a user-chosen constant. The first term of the objective affords a positive weight  $a_{ij}$  if  $(v_i, v_j)$  is not cut, and weight  $-a_{ij}$  if  $(v_i, v_j)$  is cut; the second term penalizes cluster size imbalance.

While MFA is a well-studied optimization paradigm, its application to VLSI CAD remains largely unexplored. Like many promising approaches (for instance, those based on eigenvectors, one-dimensional orderings, mathematical programming, fuzzy clustering, etc.), the MFA approach permits non-discrete partitioning solutions (i.e., a relaxation), and thus allows search over a larger solution space. As highlighted in Section 4, it is a reasonable strategy is to leave the feasible ("legal") region of the solution space, find a superior infeasible ("non-legal") solution, then find the feasible solution that is closest to the infeasible solution. However, like SA, MFA takes a long time to converge, though parallel implementations may reduce this time.

#### 3.3 Tabu Search

Tabu search was proposed by Glover [74] as a general combinatorial optimization technique. Tabu search is similar to iterative improvement in that moves are sought which transform the current solution to its best neighboring solution. Tabu search also maintains a tabu list of its r most recent moves (e.g., pairs of modules that have been swapped recently), with r a prescribed constant; moves on the tabu list cannot be made. The tabu list exists to prevent cycling near a local minimum and also to enable uphill moves; in some sense, the tabu list can be viewed as an alternative to the locking mechanism in KL and FM. Occasionally, a tabu move may be made if the aspiration function permits it (essentially, the aspiration function will override the tabu list if the move "looks good enough"). A claimed advantage of tabu search over SA is that SA may waste time making poor random moves or cycling through previously visited regions of the solution space. Although tabu search can certainly behave similarly, it is designed to quickly find a local minimum, climb out of the "valley" surrounding this local minimum, and then move on to the next local minimum. In this sense, tabu search might explore the solution space more efficiently than SA.<sup>7</sup>

Tabu search has been applied to graph bisection by Tao et al. [180] and Lim and Chee [134]. In [180], a move consists of swapping a pair of modules, and the aspiration function is one less than the cost

<sup>&</sup>lt;sup>7</sup>It is instructive to compare the motivations for tabu search with those of other methods in the optimization literature, e.g., Baum's iterated descent [21] or the "iterated Lin-Kernighan" strategy used by Johnson [109] to address the traveling salesman problem. Furthermore, one may ask whether certain problem classes possess relationships among local minima in the neighborhood structure which make tabu search more effective (e.g., see [25]).

of the best solution, i.e., a pair swap on the tabu list is accepted if the resulting solution has lower cost than every solution seen so far. The authors of [134] also adopt a pair-swapping neighborhood structure, though the aspiration function depends on the cost of the current solution. For each solution with cost F, the aspiration value A(F) is the maximum decrease in cost that has been previously observed when moving from a solution of cost F. Thus, if a move from a solution with cost F results in a solution with cost F', then the aspiration function overrides the tabu list if F - F' > A(F).

Areibi and Vannelli [9] first applied tabu search to hypergraph bipartitioning using the same aspiration function as [134], but with single module moves as the neighborhood operator. Andreatta and Ribeiro [7] applied tabu search to a DAG partitioning formulation designed for testing of combinational circuits. Areibi and Vannelli have also applied tabu search as a post-processing mechanism to initial partitioning solutions constructed using an eigenvector [10] and a genetic algorithm [8] [11]. In [8], the genetic algorithm is used to generate many good starting solutions, so that the tabu search can in some sense concentrate its efforts on the most promising regions of the solution space.

# 3.4 Genetic Algorithms

Genetic algorithms are motivated by Darwin's theory of natural selection in evolution, where "superior" members of a species produce more offspring in succeeding generations than "inferior" members [98]. A genetic algorithm (GA) starts with an initial population of solutions. This population evolves over generations, with the solutions in the current generation being replaced with a set of offspring solutions in the next generation. A GA implementation typically has crossover and mutation operators that determine candidate offspring for the next generation. The crossover operator is analogous to mating: two solutions are selected from the current population (based on some probabilistic selection scheme), and (their descriptors) are partially mixed to generate an offspring. The mutation operator enables small random perturbations to a given single solution. There exists some heuristic justification (cf. the "schema theorem" of [98]) for why such operators enable "good" solution characteristics to become more prevalent (and "bad" characteristics less prevalent) in the population with succeeding generations. The replacement scheme is the final component of a GA; it determines which offspring will replace which members of the current population. Designing each of these elements (crossover and mutation operators, selection scheme and replacement scheme) seems to be critical to the success of a genetic approach.

Inayoshi and Manderick [108] studied weighted graph bisection, representing solutions as indicator vectors having equal numbers of 0's and 1's. The Hamming distance between two solutions  $\vec{x}$  and  $\vec{y}$  is given by  $d_H(\vec{x}, \vec{y}) = ||\vec{x} - \vec{y}||^2$ , i.e., the number of entries in which  $\vec{x}$  and  $\vec{y}$  differ. The crossover operator applied to  $\vec{x}$  and  $\vec{y}$  constructs an offspring  $\vec{z}$  in which  $z_i = x_i$  if  $x_i = y_i$ ; otherwise, if  $d_H(\vec{x}, \vec{y}) = 2M$ ,

the 2M coordinates of  $\vec{z}$  in which  $\vec{x}$  and  $\vec{y}$  differ are randomly filled with M ones and M zeros. Thus,  $\vec{z}$  inherits the entries common to its two parents, and has mean Hamming distance M to each of its parents. A mutation of  $\vec{x}$  flips a random  $x_i = 1$  to 0 and a random  $x_j = 0$  to 1, yielding one of the  $\frac{n^2}{4}$  neighbors of  $\vec{x}$  according to the pair-swap neighborhood structure. The selection scheme is linear-rank based: solutions are ranked by their cost, and the probability of a solution being chosen for a mutation or crossover operation is linearly decreasing in its rank.

Ackley [1] proposed a GA for Min-Cut Bisection that combines crossover and mutation into a single operation. The crossover of  $\vec{x}$  and  $\vec{y}$  yields an offspring  $\vec{z}$  for which each entry  $z_i$  has probability p of being set to a random value, and probability  $\frac{1-p}{2}$  of being set to  $x_i$  or  $y_i$ , respectively. The selection scheme is purely random and the replacement scheme eliminates a random solution in the current population which has below-average quality. This GA may create unbalanced solutions that are not legal bisections, and therefore also incorporates a penalty term equal to  $\frac{2}{5}(||\vec{x}||^2 - \frac{n}{2})^2$  in the cost function. The structure of the cost function reflects the preference of [1] for a continuous cost function over the solution space.

Bui and Moon have utilized GAs for graph bisection [32] and for ratio cut bipartitioning of hypergraphs [31]. Their linear selection scheme is a function of solution cost instead of rank (specifically, the best solution is four times as likely to be selected as the worst solution, and a solution of intermediate quality will be chosen with probability proportional to its cost difference from the worst solution). The replacement scheme is adaptive; in general, an offspring replaces its more closely related parent (in terms of Hamming distance) if it has lower cost than the parent. The mutation operator flips each  $x_i$  value in  $\vec{x}$  with independent probability = 0.015, and crossover is accomplished via random crossover points. For example, if there are three crossover points  $1 \le c_1 < c_2 < c_3 \le n$ , then the offspring  $\vec{z}$  derived from crossover of  $\vec{x}$  and  $\vec{y}$  has  $z_i = x_i$  for  $1 \le i < c_1, c_2 \le i < c_3$  and  $z_i = y_i$  for  $c_1 \le i < c_2, c_3 \le i \le n$ . Since this crossover operator makes it likelier for  $v_i$  and  $v_j$  to be in the same cluster if |i-j| is small, ordering the problem encoding to capture the netlist structure can improve performance. The implementation of [31] adopts a weighted depth-first ordering; orderings based on the 1-dimensional representations discussed in Section 4 may be promising in this context.